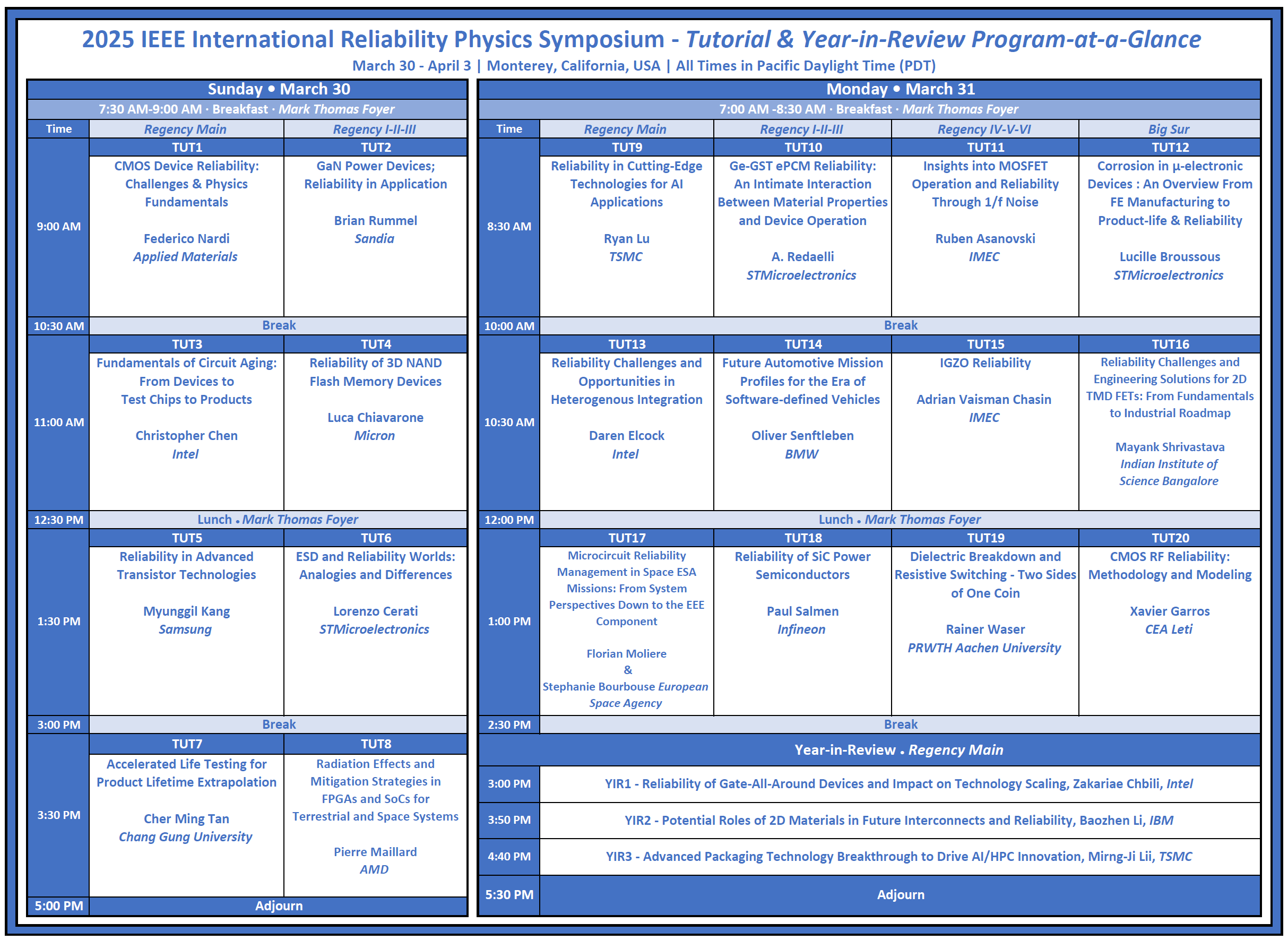

2025 Tutorials

Inside Program: Conference Program l Keynote Speakers l Tutorials

Workshops l Year in Review l Highlighted Papers | Invited Speakers

Tutorial Program at a glance

List of Tutorials

Insights Into MOSFET Operation and Reliability Through 1/f Noise

Ruben Asanovski (imec)

This tutorial delves into understanding 1/f noise in the drain current of MOSFETs, emphasizing its role in device performance and reliability. We first explore the origins of 1/f noise and its relation to random telegraph noise (RTN). Next, we present state-of-the-art noise models, critically discussing their approximations. Finally, we showcase the potential of 1/f noise as a diagnostic tool for assessing dielectric quality, particularly for advanced logic technologies and quantum computing applications.

Dr. Ruben Asanovski earned a Ph.D. in Electronics Engineering from the University of Modena and Reggio Emilia in 2024. His research focuses on 1/f noise in state-of-the-art technologies down to cryogenic temperatures. He has received several awards during his studies, including the Best Student Paper Awards at IEDM 2022, EuroSOI-ULIS 2021, and INFOS 2023. In recognition of its expertise, he was invited to speak at the ICNF 2023 conference regarding 1/f noise at cryogenic temperatures. In 2024, he joined imec as a researcher in the DRE team.

Reliability of 3D NAND Flash Memory Devices

Luca Chiavarone (Micron)

The advent of 3D NAND flash memory has revolutionized data storage technology, offering significant improvements in density, performance, and cost-effectiveness compared to traditional planar NAND. However, the reliability of 3D NAND flash memory devices remains a critical concern, requiring deep investigation depending on the field application. This tutorial provides a comprehensive overview of the reliability challenges and solutions associated with 3D NAND flash memory devices.

Luca Chiavarone received the Ph.D. degree in physics from University of Bari, Italy, in 2000, with a thesis on the study of the optical properties of conjugated polymer thin films and the fabrication of electroluminescent organic devices. In 2000, he joined the Non-Volatile Memory Process Development Group, STMicroelectronics, Agrate Brianza, Italy, working on electric wafer sort and on the characterization, reliability and multilevel applications of Flash cells. In 2010 he joined Micron Technology, Vimercate, Italy, under Technology Development Group. He is currently SMTS - NAND Reliability, dealing with Flash memory physics, technology, and reliability modeling.

Reliability in Cutting-Edge Technologies for AI Applications

Ryan Lu (TSMC)

The rise of advanced silicon and packaging has increased the demand for HPC in AI applications, where any malfunction can be disruptive due to the many HPC units running simultaneously. Key factors include superior computing power efficiency, low DPPM, thermal management, and balanced packaging stress. Ensuring product robustness requires a thorough understanding of reliability. This tutorial covers transistor-level and package-level reliability. Additionally, DPPM management and future reliability challenges will be addressed in this AI era.

Dr. Ryan Lu is a Director in the TSMC Quality and Reliability organization, supervising reliability development and customer engagement across all silicon, specialty, and packaging technologies. He received his Ph.D. degree in Electrical Engineering from UCLA in 2004. From 2004 to 2013, he worked in Intel's QR organization. Since 2013, he has been a part of TSMC's QR organization, and he is currently supervising a reliability team of more than 300 engineers. Dr. Lu has more than 20 years of experience in the QR area and has authored or co-authored many conference and journal publications on reliability topics.

Accelerated Life Testing for Product Lifetime Extrapolation

Cher Ming Tan (Chang Gung University, Taiwan)

**Product lifetime** is a critical attribute of any technical product, as it directly influences the perceived value and long-term cost-effectiveness of the product. Meeting high product reliability standards often necessitates extensive testing to accurately predict the product's lifetime, a process that can be time-consuming. Consequently, accelerated life testing (ALT) is widely adopted to shorten the testing period. However, to ensure the reliability and accuracy of the lifetime prediction, a suitable extrapolation method must be selected based on the acceleration model. Unfortunately, identifying the most appropriate acceleration model for different failure mechanisms is a complex task, and conventional models commonly used in industry may not always be suitable. This tutorial will cover various acceleration models, discussing their applications and selection criteria for different types of failure mechanisms.

While acceleration models are primarily used to determine the acceleration factor, it is essential to use this factor effectively to perform accurate extrapolation. Traditionally, extrapolation is performed using a single reliability index, such as Mean Time to Failure (MTTF). However, a more comprehensive approach involves extrapolating the entire reliability function, a process known as two-dimensional extrapolation. This tutorial will provide an in-depth explanation of how to perform this two-dimensional extrapolation to ensure a more accurate and meaningful lifetime prediction.

For products requiring exceptionally high reliability, even accelerated life testing may not suffice due to the extended timeframes involved. In such cases, accelerated degradation testing (ADT) is increasingly employed. However, a common pitfall in ADT is the use of simple curve fitting methods to estimate failure times, which can lead to significant errors in lifetime prediction. This tutorial will present an example of proper extrapolation techniques in accelerated degradation testing to demonstrate best practices for accurate lifetime estimation.

Dr. Tan, a graduate from the University of Toronto, has vast expertise in electronic reliability (industry and academic), with over 400 publications and 14 books. He served at Nanyang Technological University (1996–2014) and now leads the Research Center on Reliability Sciences at Chang Gung University, Taiwan. An editor for journals like Scientific Reports and IEEE TDMR etc, he is also an IEEE Distinguished Lecturer. Recognized among the top 2% of scientists by Stanford University, he holds Fellow status with multiple international engineering organizations. He was elected the 1st President of the Taiwan Reliability Technology Association..

Ge-GST ePCM Reliability: An Intimate Interaction Between Material Properties and Device Operation

Andrea Redaelli (STMicroelectronics)

Among the emerging memories that can be integrated in the back end of the line, phase Change Memory (PCM) is emerged as one of the most interesting for embedded applications below 28nm node. The interplay between active material behavior and device operation is fundamental to mastering the technology. In the tutorial, the effect of the electrical operations done on the device are studied at the material level, clarifying the relationship between applied programming pulse, final microscopic phase and composition. The reliability of the technology is then discussed within this framework, highlighting some fundamental trade-offs between retention, cycling and retention after cycling. For the retention, the effect of Ge introduction on the crystallization incubation time will be discussed and, for endurance, the material aging effect. (i.e. compositional shift) is highlighted as a key mechanism to be mastered. Finally, the optimization done at process level to achieved automotive grade qualification will be discussed.

Andrea Redaelli received the Laurea and Ph.D. degrees in electronic engineering from the Politecnico di Milano, Italy, in 2003 and 2007 respectively. During the Ph.D., he worked on Phase Change Memories in the Department of Electrical and Electronic Engineering (Politecnico di Milano), collaborating with the Non-Volatile Memory Technology Development Group of STMicroelectronics, Agrate Brianza. From 2007, he joined STMicroelectronics working on advanced technologies for Non-Volatile memories. From 2008 to 2013 he worked as cell lead engineer on 45 and 26 nm PCM technology developments, firstly as a Numonyx employee and then joining Micron Technology. In the same years, Andrea cooperated with the Department of Electrical Engineering, Politecnico di Milano, in holding master classes on electronics and signal conditioning. His work areas included memory array architecture definition, design of test structures, process integration, cell operation modelling and cell electrical testing. He was also the coordinator of a European funded project under FP7 named PASTRY on low power PCM development. From 2014 to March 2020, Andrea worked on 3DXpointTM technologies, in charge of the cell development at the most advanced scaled nodes. Since April 2020, Andrea is a fellow in STMicroelectronics, leading the cell development of embedded PCM technologies and for AI applications. Andrea is author and co-author of more than 70 papers and more than 140 US patents, resulting in a h-index of 32 according with google scholar.

Dielectric Breakdown and Resistive Switching – Two Sides of One Coin

Rainer Waser (RWTH Aachen University)

Depending on the dielectric material and geometry, several dielectric breakdown mechanisms can be distinguished. In their final phase, they all lead to a thermal runaway. The initial phase is a completely electronic process, immediately followed by ion movement. This is identical to the electroforming process in resistive switching. To prevent a permanent destructive breakdown, the current during this process must be limited either by a series resistor or an ultra-fast current control.

Rainer Waser received his PhD in physical chemistry at the University of Darmstadt in 1984, and worked at the Philips Research Laboratory, Aachen, until he was appointed Professor at the faculty for Electrical Engineering and Information Technology of the RWTH Aachen University in 1992 and director of the Institute for Electronic Materials at the Forschungszentrum Jülich, in 1997. In 2007, he has been co-founder of the Jülich-Aachen Research Alliance, section Fundamentals of Future Information Technology (JARA-FIT). In 2014, he received the Leibniz Prize of the German national science foundation (DFG) for his work on the phenomenon of redox-based resistive switching.

Future Automotive Mission Profiles for the Era of Software-defined Vehicles

Oliver Senftleben (BMW)

The demand for automotive mission profiles enabling a detailed reliability assessment for all utilized semiconductor and device technologies is continuously increasing due to new lifetime requirements for zonal architectures and fully electric autonomous software-defined vehicles (SDV).

The tutorial will focus on these new challenges and will present a new hierarchical approach to define EMPs for various applications, installation spaces and climate zones wrt. temperature, temperature swing and humidity.

Oliver Senftleben holds a master's degree in physics and a PhD in electrical engineering. Since 2011 he has been working as a Senior Technical Expert for Semiconductor Technologies at AUDI AG and is currently responsible for wide band gap power devices and mission profiles within the department for Semiconductor Strategy at BMW Group in Munich.

As a part of his responsibilities he is representing BMW towards the Automotive Electronics Council, is member of the ECPE AQG 324, German VDA 210-200 (Hardware Delta-Qualification) and German VDE 5.7 working group on Extended Mission Profiles.

ESD and Reliability Worlds: Analogies and Differences

Lorenzo Cerati (ST Microelectronics)

Reliability assessment of Integrated Circuits and the definition of their robustness when exposed to Electrostatic Discharge (ESD) events show many commonalities but also meaningful differences in the adopted stress methodologies and theoretical modelling approaches. This tutorial will first focus on the ESD stress testing methods and on the international standards (Human Body Model, Charged Device Model…), which define the basic rules of this field. Differences between device-level and system-level assessments will be analyzed to determine the actual threat that any IC may be exposed to during its entire lifetime. The basic approaches to implement an effective ESD protection network will be presented, identifying the key physical and electrical parameters. Finally, the various characterization techniques adopted by ESD engineers will be shown, highlighting the numerous analogies with the reliability investigations and the also the important differences between the two worlds. Degradation mechanisms and physical failures peculiar for each of these fields will be discussed.

Lorenzo Cerati is reliability, ESD and CPI (Chip-Package Interaction) Technical Director for Smart Power Technologies and Fellow of the Technical Staff at STMicroelectronics. Lorenzo received his M.Sc. degree in telecommunication engineering at the "Politecnico di Milano" Technical University in 1998, discussing a thesis on a CdZnTe cross-connect for optical networks. Since 2000, Lorenzo has been working in STMicroelectronics, starting as ESD protections development engineer for Smart power technologies (BCD). Lorenzo has led the group responsible for ESD protections development, Latch-up immunity and bipolar parasitic analysis in BCD processes for about 15 years and represented STMicroelectronics in the ESDA standardization committees, including HBM, CDM and TLP, where he also acted as vice-chairman. From 2016 to 2023 he served as member of the ESDA Technical and Advisory Support Committee (TAS), ESDA Board of Directors and acted as co-chair of the Standards BU. Since 2022 Lorenzo has been leading the team responsible for the qualification of BCD technologies in STMicroelectronics.

Lorenzo served multiple times as a member of the ESREF, ICICDT, IRPS, IEW, and EOS/ESD Symposium Technical Program Committees and authored several papers on ESD and EDA topics. Lorenzo was General Chair at the 2020 EOS/ESD symposium and chaired the ESD&LU session at the 2024 IRPS.

Corrosion in µ-electronic Devices : An Overview From FE Manufacturing to Product-life & Reliability

Lucile Broussous (ST Microelectronics)

In this tutorial, first general concepts will be provided about Corrosion, based on elemental "corrosion Triangle", then focus will be done on fundamentals properties of metals and materials used in microelectronics. First part will focus on corrosion in Front End and Backend Manucaturing. Then Corrosion mechanisms in product life and reliability risks will be explored for different technologies. At least a focus will be done on Devices robustness assessments and Corrosion prevention.

Dr. Lucile Broussous, received a PhD in physical-chemistry in 1999, at the University of Montpellier. She joined STMicroelectronics in 2001 as an R&D process engineer.

From 2001 to 2018, she acquired a strong experience on surface preparation, cleaning, materials for interconnections. In 2018, she joined the Chip to Package Interaction team, and enlarged her technical knowledge to Assembly processes and Reliability. She was involved in the qualification of Image sensors and CMOS technologies for different applications and missions profiles.

Collaboration with Universities focused on metals corrosion in solution, contamination, porous dielectrics porosity measurements, with a specific focus on product reliability.

Fundamentals of Circuit Aging: From Devices to Test Chips to Products

Christopher S. Chen (Intel)

This tutorial will provide an overview of how transistor aging affects circuit performance and reliability. We will begin with an overview of various device aging mechanisms and demonstrate how they manifest at the circuit level. Next, we will cover how these aging mechanisms are characterized using silicon test structures and modeled in circuit simulations. Finally, we will discuss how circuit aging can be measured on test chips to help predict the reliability of semiconductor products.

Christopher Chen is a circuit reliability engineer with Intel. He holds a B.S. in EECS from UC Berkeley and an M.S. in EE from UCLA. He began his career as a device characterization engineer with Altera and joined Intel in 2015 via acquisition. During his 18 years with Altera and Intel, Chris has held various roles focusing on foundry interface, technology development, device engineering, parametric test, and transistor reliability. Throughout this time, he has consistently worked on the design and characterization of test structures for assessing technology performance, reliability, and variability. Chris has published 15 papers and holds 3 patents.

CMOS RF Reliability: Methodology and Modeling

Xavier Garros (CEA Leti)

The growing need for connectivity has significantly driven the RF component market forward. Consequently, in CMOS technologies, RF functions have been added to purely digital circuits to enable communication functions. The issue is that transistors were not originally designed for RF but solely for digital applications. This raises significant reliability issues for several reasons: (1) the operational mission profile of an RF transistor is often much more demanding than that of a digital transistor, and (2) certain aging mechanisms either emerge or are altered at high frequencies, requiring aging characterization directly under RF stress conditions and a reevaluation of reliability models to account for high-frequency specifics. In this tutorial, we propose to study in detail the reliability of devices under RF stress conditions. First, we will address the challenges of RF aging characterization at the wafer level, offering a clear methodology to achieve robust and relevant results. Then, we will discuss the various possible approaches to model the reliability of RF components. Finally, the impact of high frequencies on degradation mechanisms will be examined, with a particular focus on oxide breakdown.

Xavier Garros is a senior scientist in the Electrical Characterization Laboratory of the CEA-LETI. He received his Ph.D. from the University of Marseille, France (2004), on the physics and electrical properties of High-K dielectrics. He has a deep knowledge in electrical characterization, physics and modeling of the reliability concerns in advanced technologies (Bulk, FDSOI, Nanowire). Recently he also addresses other research fields like circuit and RF reliability. He supervised and is supervising 9 thesis so far. He wrote, as author and co-author, 3 patents and more than 100 papers in international conferences and journals about CMOS reliability physics. He is also involved in the program committee of famous international conferences in that field (IEDM, IRPS, SISC..).

CMOS Device Reliability: Challenges and Physics Fundamentals

Federico Nardi (Applied Materials)

We will discuss the advanced logic technology roadmap and device reliability constraints for both Front-End-of-Line (FEOL) and Back-End-of-Line (BEOL) processes. Then we will delve into the physics of device reliability from an atomic defect perspective, focusing on defect trapping and generation, and covering key reliability issues such as Bias Temperature Instability (BTI), Self-Heating Effects (SHE), Breakdown/Time-Dependent Dielectric Breakdown (BD/TDDB), and Electromigration (EM), with a focus on BD characterization and modeling. Additionally, we will discuss the challenges in characterization, including the transition from accelerated tests to real operating conditions and the shift from simple test vehicles to complex 3D devices. We will emphasize the role of physical modeling, with a focus on connecting process steps to material properties and predicting device and circuit behavior based on these properties.

Federico Nardi is Director of Applications Engineering in the Systems-To-Materials group at Applied Materials. He has more than 12 years of experience in managing and leading technical teams in multinational corporations (Intermolecular, SanDisk, Western Digital), spearheading the product development of new technologies and unique TCAD software solutions for electronic device simulations. With his background in Electrical Engineering (Ph.D. from Polytechnic of Milan) he is able to guide the technology development by relating electronic device performances with material science, process integration, circuit design and simulation. He has experience in the development of in-memory computing accelerators and in the exploration of machine learning enhanced TCAD solutions. He created unique intellectual properties (28 granted patents), authored and coauthored more than 35 papers published in international journals and proceedings, presented at multiple international conferences with more than 3000 citations (h-index 22).

Reliability of SiC Power Semiconductors

Paul Salmen (Infineon)

This tutorial will give an overview on the field of reliability of SiC power semiconductors. The first part will cover gate oxide related fails due to extrinsic/intrinsic defects and the SiC specific failure mechanism gate switching instability. In the next section, the tutorial will focus on everything related to the edge termination, especially humidity induced degradation of SiC devices. The last part will then deal with degradation mechanisms related to the bulk SiC crystal. Here, degradation of electrical parameters (namely bipolar degradation) as well as thermomechanical stress like power cycling are driven by the properties of the SiC crystal. Where available, the tutorial will also show which topics are addressed by already published JEDEC documents.

Dr. Paul Salmen is working currently as principal for reliability of SiC power semiconductors in the division green industrial power at Infineon technologies. He received his PhD in physics at the TU Dortmund university in 2017 and is, since then, working at Infineon technologies on SiC reliability. His work focuses on understanding the degradation mechanisms of SiC power devices and their chip-package-interaction with a focus on modules.

Microcircuit Reliability Management in Space ESA Missions: From System Perspectives Down to the EEE Component

Florian Moliere and Stephanie Bourbouse (European Space Agency)

The aim of this tutorial is to present the microcircuit reliability activities set up in Space programs to guarantee the success of the space missions from the spacecraft system level down to the EEE component.

Space business is characterized by a large range of applications that are most of the time custom made and have the specificity to operate in harsh and non-standard environments. In this context, the success of those missions strongly relies on the ability of electronics units and their EEE components to fulfil their function without anomaly all along their service time in their specified mission environment. To support this goal, the right part evaluation, selection, qualification and risk mitigations of Electronic, Electric and Electromechanical EEE parts and more especially of microcircuits are of major importance.

The aim of this tutorial is to present the microcircuit reliability activities set up in Space programs to guarantee the success of the space missions from the spacecraft system level down to the EEE component. First, this tutorial will introduce the ESA Mission classification system providing an overview of Earth Observation, Navigation, Telecommunication, Science and Human Robotics Exploration missions detailing their specific environments and their reliability requirements. Next, the tutorial will focus on the product assurance activities related to the digital microcircuits implemented in space programs that comprise reliability analysis (as part of RAMS), EEE quality, radiation evaluation and design mitigation. Finally, a specific section devoted to use of ultra deep sub-micron IC technologies in space programs and their related wear out management will be presented and discussed.

Dr. Florian Moliere is EEE expert at European Space Agency (ESA/ESTEC). He acts as both project support for earth-observation, science, human robotic and robotic exploration mission programs and microcircuit specialist. He holds both an Engineering degree in Electronics from ISEN -Toulon in 2007 and a Ph.D in Microelectronics from the University of Aix-Marseille in 2011. Moreover, Florian has 17 years of experience in aeronautics and space industry within Airbus Group (formerly EADS) in Paris (France) as EEE technologist and reliability engineer, and within Airbus Defence and Space in Friedrichshafen (Germany) as EEE engineer for project support and Product Assurance Manager.

Stephanie Bourbouse is a Dependability and Safety engineer at the European Space Agency in the Netherlands (ESA/ESTEC). She graduated from both ESIGELEC (France) and Dublin City University (Ireland) with a master’s Degree in Electronics and Telecommunications. She worked for 18 years in the Space industry for a Space Prime integrator (Airbus Defence and Space) before joining ESA, first performing reliability and safety analyses at EEE board and unit levels, and then at system level (instrument, satellite and constellation). Throughout her career both in the industry and ESA, in parallel to her activity on projects (Military and Civil Earth Observation, Planetary exploration and Telecommunications) she has been involved in Research and Development on reliability of electronics components, in particular on how to perform quantitative and qualitative assessments at board, unit and system level, based on the observation of failures mechanisms at part level. She leads the adaptation for Space of the FIDES reliability calculation method within the European Space community and is currently involved in a Working Group to prepare a Handbook to be used by the industrials.

GaN Power Devices; Reliability in Application

Brian Rummel (Sandia)

Electrical power conversion systems are adopting next-generation technologies to meet the ever-increasing demands for higher power densities. The GaN High Electron Mobility Transistor (HEMT) has proven to be a promising candidate to increase conversion efficiencies in electrical systems. HEMTs can support higher currents, temperatures, and frequencies compared to Si-based transistors, making them suitable for power conversion applications related to electric vehicles, phone chargers, grid-edge technologies, data centers, and many more. This tutorial covers the applicability of GaN HEMTs in a variety of power conversion systems, design for reliability considerations at the device level, and reliability concerns for high-power applications.

SNL is managed and operated by NTESS under DOE NNSA contract DE-NA0003525

Dr. Brian D. Rummel earned a Ph.D. in Microsystems Engineering from the University of New Mexico in 2021. In 2022, he joined Sandia National Laboratories, where he is now a Senior Member of Technical Staff. His research at Sandia is primarily focused on wide-bandgap (WBG) materials research and reliability testing to support next-generation power transistor technologies. His most recent focuses have included WBG-MOS interface characterization, low-temperature hot-carrier degradation in GaN HEMTs, and improving radiation resilience in high-k dielectrics. At Sandia, Brian has helped to assemble the Power Electronics Reliability Laboratory and intends to broaden Sandia’s testing capabilities to study state-of-the-art power electronics reliability challenges.

IGZO Thin-Film Transistor Reliability: the Last Roadblock for Memory Applications

Adrian Chasin (imec)

The main goal of this tutorial is to elucidate the main reliability mechanism currently limiting the deployment of amorphous semiconducting oxides for memory applications (specifically DRAM). Firstly, we will delve into the material properties of the main player in the amorphous oxide semiconductor (AOS) realm: Indium-Gallum-Zinc oxide (IGZO). We will explain the multitude of applications envisaged for this material and how it could enable the development of 3D-DRAM. Secondly, we explain how optimizing the device architecture enables it to meet the stringent off and on currents required for DRAM application. Finally, the details of BTI in IGZO will be explained, focusing on the interplay between electron trapping into pre-existent gate-dielectrics and the H-doping mechanism. Technology mitigations for these degradation processes will be explained.

Adrian Chasin is a Principal Member of Technical Staff (PMTS) and the R&D team leader of the FEOL Reliability team at imec. He is involved in several logic/memory projects ranging from advanced devices architectures through new memory concepts to use of non-conventional semiconducting materials. He received the PhD in Electrical Engineering from the University of Leuven in 2014, when he developed devices based on new semiconducting oxides for display and flexible electronics, targeting RF applications. After working at NXP on modelling/evaluation of CMOS technologies, he joined the imec reliability group in 2015 as a researcher. His main research interests are FEOL/MOL reliability in advanced CMOS technologies and thin-film devices for memory and BEOL applications. He authored and co-authored more than 150 publications.

Radiation Effects and Mitigation Strategies in FPGAs and SoCs for Terrestrial and Space Systems

Pierre Maillard (AMD)

FPGAs and SoCs are well-suited for complex designs and evolving algorithms in terrestrial and space applications, especially compared to ASICs. This tutorial covers SRAM and non-volatile FPGA architectures, their evolution into modern Adaptive SoCs, and mechanisms behind Single Event Effects (SEE) and Total Ionizing Dose (TID). It includes error classifications, mitigation strategies, testing methods, and results. We’ll also explore how Functional Safety, RAS, and AI/ML applications have impacted SEE testing and mitigation. The final section addresses challenges and solutions for next-gen markets, including telecom, automotive, data centers, avionics, and defense sectors.

Dr. Pierre Maillard leads the Radiation Effects & RAS Solutions team at AMD’s Adaptive Embedded Computing Group (AECG), focusing on the architecture, development, and validation of radiation-tolerant FPGA/SoCs solutions for markets such as Telecom, Avionics, Automotive, Datacenters, AI, and Space. A Senior Member of IEEE, he has over 20 publications and presentations in industry-leading conferences and journals, along with more than 20 issued patents in radiation effects on electronics. Dr. Maillard holds M.S. and Ph.D. degrees in Electrical Engineering from Vanderbilt University and an M.S. from the University of Montpellier II.

Reliability in advanced transistor technologies

Myunggil Kang (Samsung)

The growing usage of mobile products and high-performance computing devices, such as smartphones, wearables, and HPC servers, has created a demand for continuous enhancements in power, performance, and area. To meet these market requirements, logic technology has evolved over the years, with traditional planar Si-MOSFETs successfully following Moore's law through the adoption of various technical innovations including stress engineering, high-k metal gate, FinFET, and GAA MBCFET.

However, the continued scaling of Tinv with high-k metal gate and the introduction of new structural changes like Fin and GAA nanosheet active have presented challenges in front-end of line (FEOL) reliability. One particular issue is the reduction in thermal dissipation paths due to fully depleted device structures, leading to significant self-heating behavior and increased vulnerability to hot carrier degradation (HCD).

In this tutorial, we will delve into the advanced device reliability issues that arise from these technological advancements. We will explore the challenges and considerations in ensuring the reliability of these devices. Furthermore, we will discuss potential successor technologies to GAA MBCFET, examining their reliability implications and how they aim to address the current FEOL challenges.

Myunggil Kang received his Ph.D. in electronic engineering from Korea University, Korea, in 2011, with a thesis focused on the study of one-dimensional nano devices. Since then, he has been working as a device engineer in the 20nm planar, 14nm FinFET, and 10nm FinFET device development group at Samsung Electronics, with a primary focus on device performance and reliability. From 2016 to 2017, he worked as an IBM JDA member in Albany, specifically working on GAA nanosheet devices. Currently, he holds the position of device leader in the 1.4nm technology development team, where he is responsible for overseeing device performance and reliability. Myunggil Kang is actively involved in the field and has joined the advanced logic technology sub-committee as a member of the IEEE-IEDM for the years 2021-2022.

Reliability Challenges and Opportunities in Heterogenous Integration

Daren Elcock (Intel)

Over the last decade, integrated circuit packaging has evolved from a simple flip chip architecture to more complex 2.5D and 3D architectures. The new architectures require many new interfaces, materials and processing which offers unique opportunities and challenges for the co-optimized package IC (CPIC) design for both performance and reliability. This tutorial will provide an overview of the transformation of packaging and the trade-offs between some of the leading architectures. Specific focuses will include reliability challenges and design for reliability.

Daren Elcock is a Senior Technical Staff Member at Intel’s Foundry Quality and Reliability team, focused on Assembly Test Packaging Technology. Over the last decade, he has worked on a variety of packaging architectures including Multi-chip Packaging, EMIB, FOVEROS, COEMIB and HBI. Daren holds a Ph.D. in Mechanical Engineering from Rensselaer Polytechnic University, New York, USA.

Reliability Challenges and Engineering Solutions for 2D TMD FETs: From Fundamentals to Industrial Roadmap

Mayank Shrivastava (Indian Institute of Science)

Transition metal dichalcogenides (TMDs) have emerged as promising materials for next-generation nanoelectronics, offering superior electronic, sensing, optoelectronic and quantum properties. However, their integration into commercial technologies is hindered by reliability challenges, including intrinsic defect-induced variability and degradations, dielectric instability, high-field degradation, and thermal management uncertainties. This tutorial provides a comprehensive overview of the reliability aspects of 2D TMD-based field-effect transistors (FETs), addressing the origin of reliability concerns, their impact on device and circuit performance, and strategies for improvement. Key topics include nature of defects and defect passivation, strain effects, contact & dielectric optimization and associated reliability challenges, lithography-induced degradation, high electric field effects, impact ionization, avalanche breakdown, hot-carrier effects, inverse piezoelectric effects and channel degradation and material level reconfiguration. The tutorial will also delve into state-of-the-art performance benchmarks and industrial scalability challenges, aiming to equip researchers and engineers with actionable insights to enhance the reliability and commercial viability of 2D TMD devices, while outlining a roadmap for their heterogeneous integration into next-generation electronics.

Prof Mayank Shrivastava is a Full Professor at the Indian Institute of Science, Bangalore, and co-founder of AGNIT Semiconductors Pvt. Ltd., which is a deep-tech start-up in the semiconductor space. He is also instrumental in setting up Gallium Nitride prototyping Fab worth $50M. He received his Ph.D. degree from the Indian Institute of Technology Bombay. For his Ph.D. work, he received Excellence in Research award and the Industrial Impact award from IIT Bombay in the year 2010. He joined the Indian Institute of Science as a faculty member in the year 2013. Prior to joining IISc, he held positions in Infineon Technologies, Munich, Germany; Infineon Technologies, East Fishkill, USA; IBM Microelectronics, Burlington, USA; Intel Mobile Communications, Hopewell Junction, USA; Intel Corp, Mobile and Communications Group, Munich, Germany, between 2009 and 2013.