Highlighted Papers

Inside Program: Conference Program l Keynote Speakers l Tutorials

Workshops l Year in Review l Highlighted Paper l Invited Speakers

(2C.1 - GaN) 10.40 am, March 24th

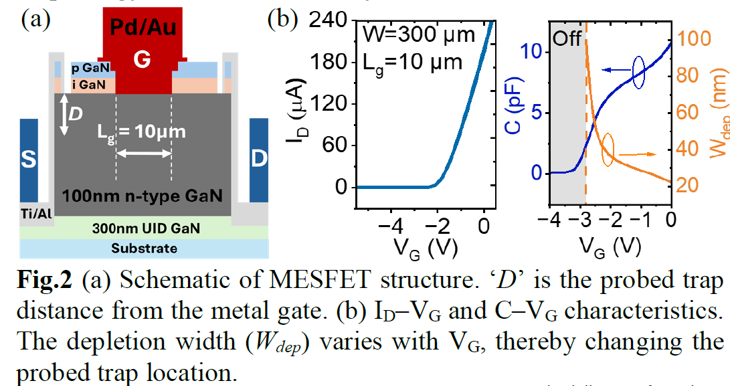

Revealing Bulk Trap Distributions in GaN MESFETs through Re-defined AC-Gₘ Characterization Method under Irradiation and Stress

Redefined AC transconductance (AC-Gₘ) technique for GaN MESFETs, enabling direct extraction of bulk trap energy, spatial location, and density

The method is applied to devices under heavy-ion irradiation and off-state stress, yielding comprehensive 3D trap maps

(2C.2 - GaN) 11.05 am, March 24th

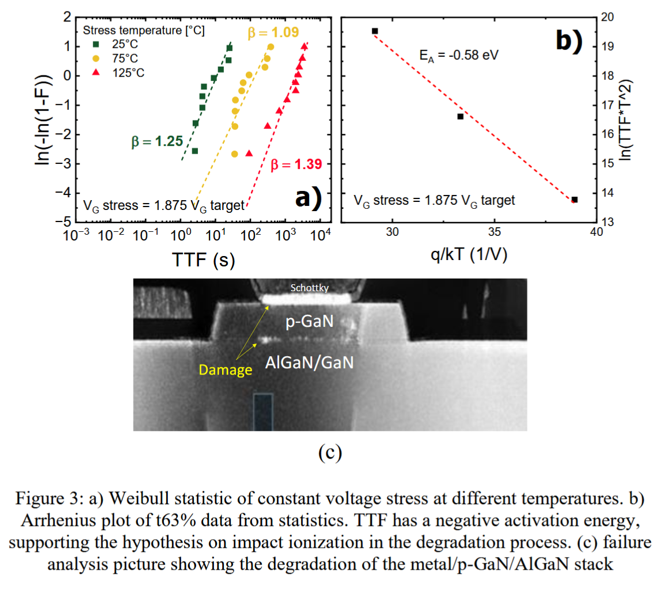

Methodology for Extrapolating the Lifetime of GaN HEMTs with p-GaN Gate

Constant voltage stress data used to extrapolate the lifetime for GaN HEMTs with p-type gate.

The model was compared with other results present in literature, confirming that: 1) the conventional E-model is not able to model the gate lifetime; 2) impact ionization (i.i.) has a role in failure mechanism, 3) Failure is ultimately driven by the presence of hot carriers in the p-GaN layer

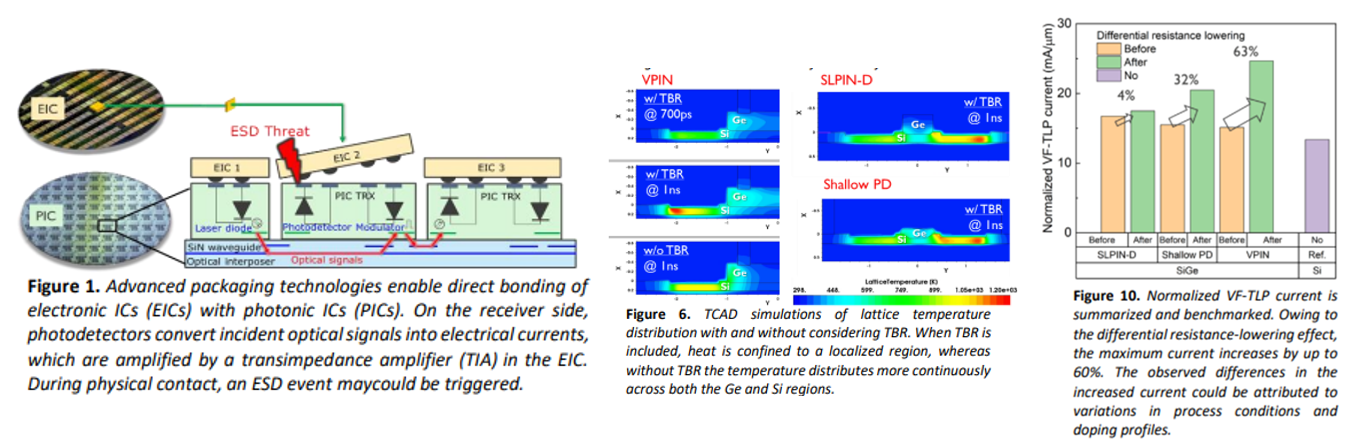

(3B.1 – EL) 1:30 PM, March 24th

Differential Resistance Lowering Effect in High-Speed Ge Photodetectors During Nanosecond ESD Events

Discussion of ESD protection challenges in photonic technologies

Analysis includes measurements and a detailed TCAD analysis.

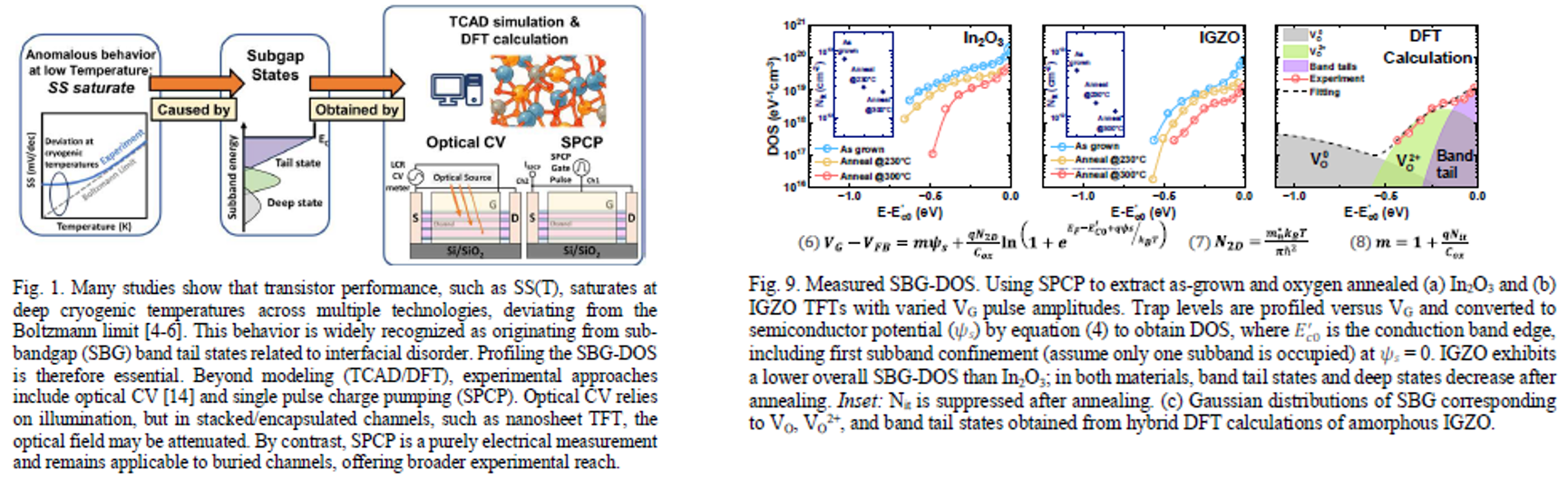

(3C.1 - RT) 1:30 pm, March 24th

Fast, Optics-Free Extraction of Interface Trap and Subgap DOS in Amorphous Oxide TFTs Using Single Pulse Charge Pumping

This paper is a comprehensive study, including a rapid but valuable SPCP testing technique, testing data, bandgap analysis, calculation, and physical model.

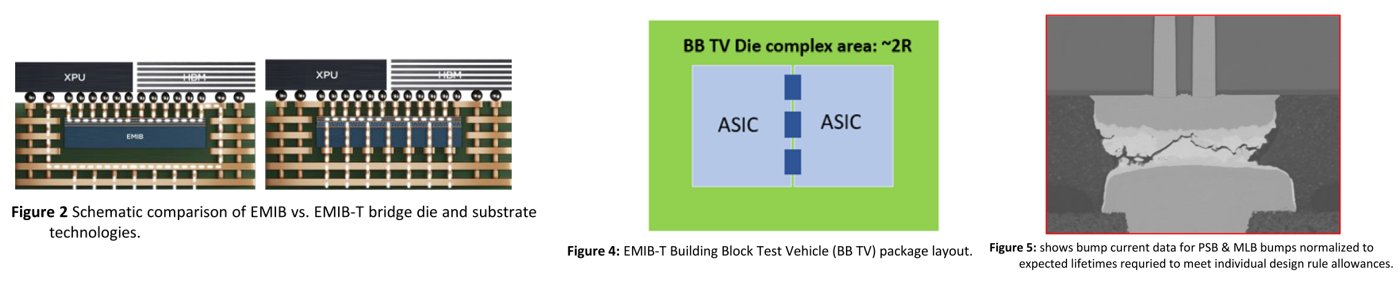

(4A - PK) 4:00 pm, March 24th

Quality & Reliability Characterization of EMIB-T (TSV) Advanced Packaging Technology

The authors performed several Thermo-mechanical reliability tests, and the results are quite satisfactory. Demonstrates JEDEC level reliability and identifies important solder joint improvement paths

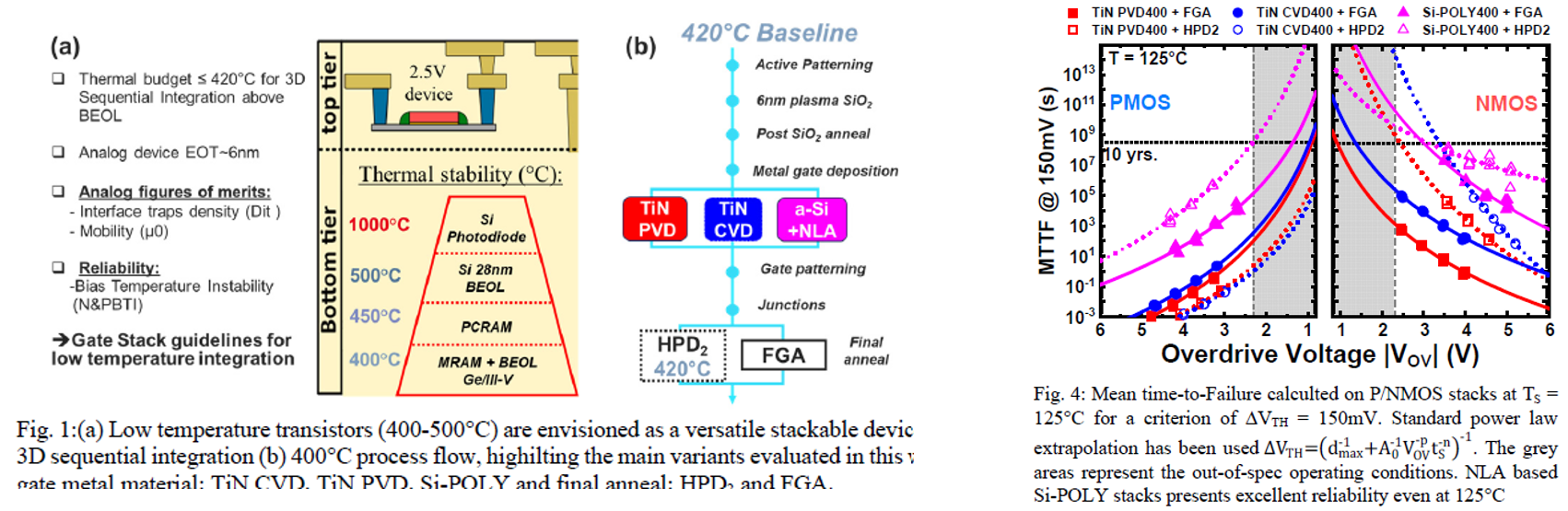

(4C.1 - PI) 3:35 pm, March 24th

Reaching the BTI 10yrs Lifetime for 2.5V BEOL Compatible (<420°C) High Voltage Si-CMOS

This paper presents a 2.5V BEOL-compatible Si-CMOS transistor using poly Si gate with UV nanosecond laser annealing that achieves a 10-year BTI lifetime at 420°C, outperforming TiN gates in reliability through effective defect passivation.

(6B.1 - NCR) 10:50am, March 25th

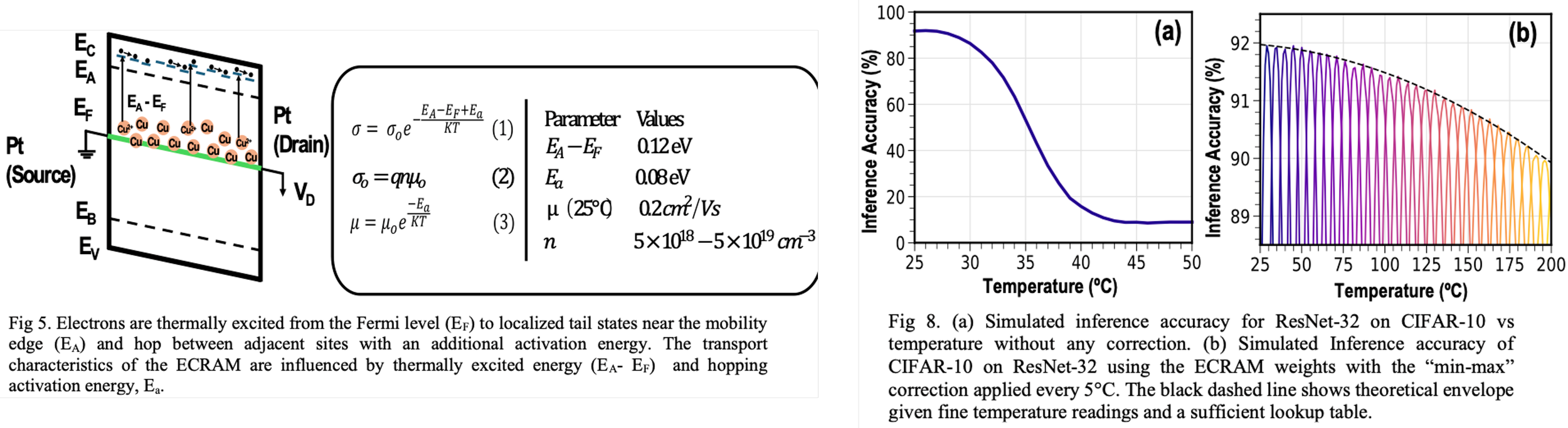

Effect of ECRAM Temperature-Dependent Conductance on Analog In-Memory Computing Inference Accuracy

Characterized Electro-Chemical Random-Access-Memory (ECRAM) temperature-dependent conductance and developed a transport model to be used in neural network inference simulation

Mitigated the impact of ECRAM temperature-dependency on analogy AI inference accuracy with a temperature-aware scaling technique, and restored accuracy in a demonstration of ResNet-32 on CIFAR-10 dataset

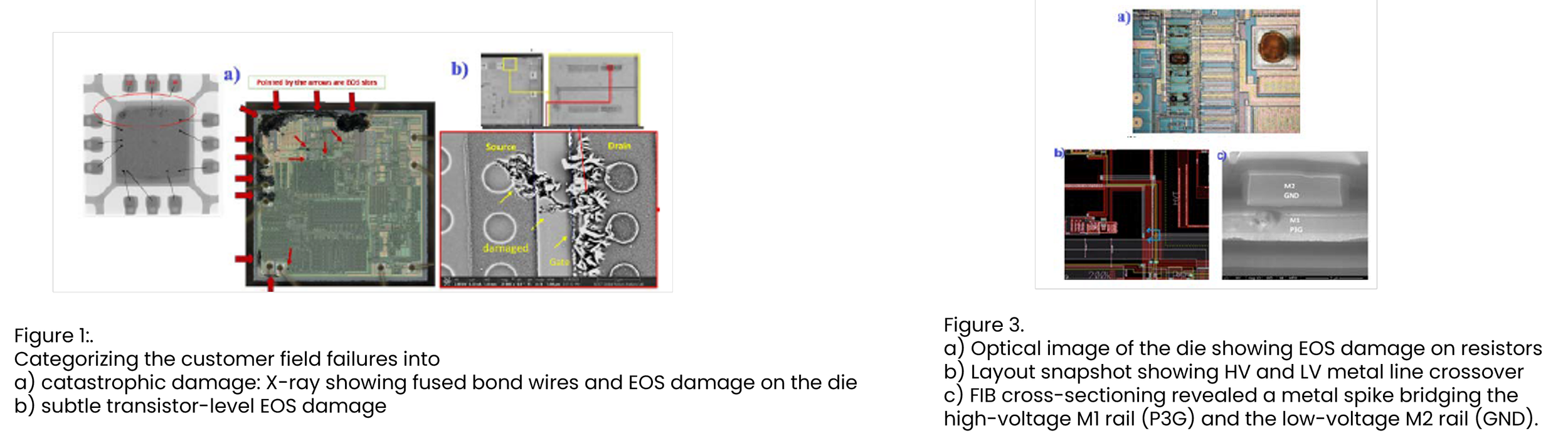

(6C.2 - FA) 11:15am, March 25th

EOS to ILD Fix: Uncovering the Hidden Culprit in High-Voltage IC Failures

Review of the full engineering journey: from initial confusion to final resolution

Explores the development of a predictive risk model based on electric field acceleration

Process fix and qualification strategy are described, including the design of experiments and reliability testing

Highlight of the collaborative engineering effort and reflection on broader lessons learned for future risk mitigation

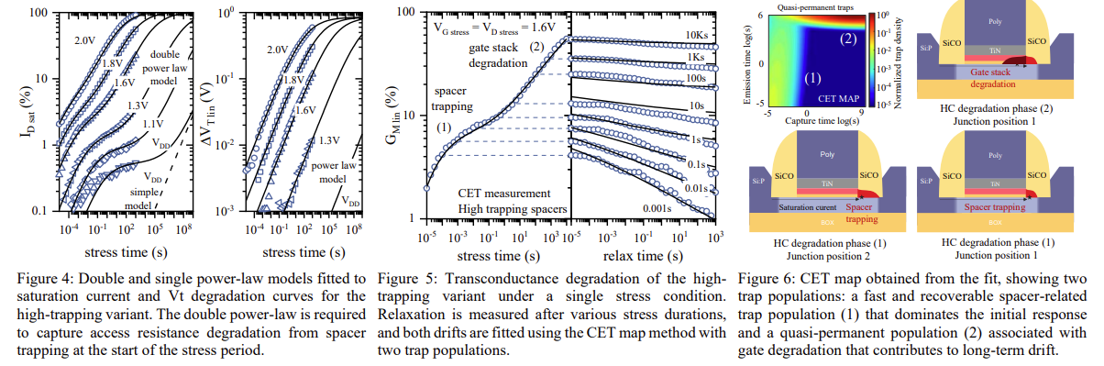

(7A.2 - TX) 1:55pm, March 25th

Spacer trapping effect on hot carriers’ degradation dynamics for advanced FDSOI nodes

This work uniquely identifies early fast‑trap behaviour in SiCO spacers and shows it does not affect long‑term reliability. It introduces an effective annealing step that nearly eliminates hysteresis. Results are consistent across NMOS and PMOS, confirming robust, scalable integration.

(8B.1 - RER) 4:00pm, March 25th

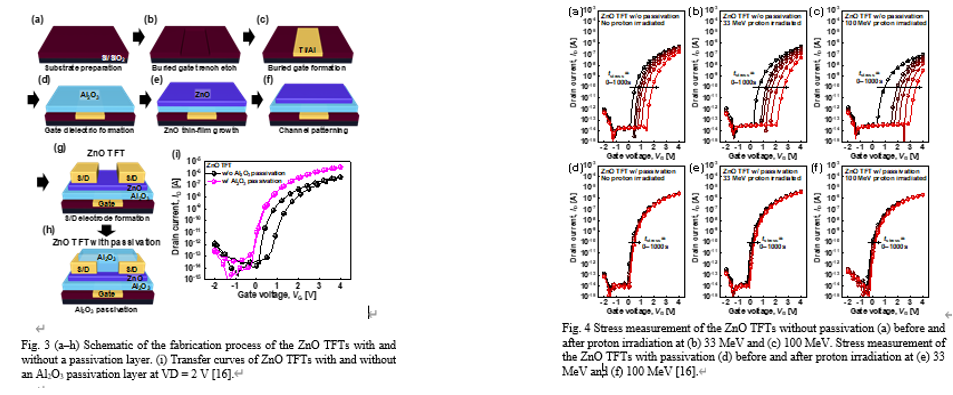

Radiation Induced Instability Mechanism and Hardening Method of Nanoscale Devices

The mechanism of gamma-ray irradiation on the electrical variations of molybdenum disulfide (MoS2) field-effect transistors with a buried local-back gate structure

The radiation hardness of high-energy protons (upto 100 MeV) in 3.5nm thickness of ZnO TFTs

Radiation hardness of the nanoscale device increased by the interface engineering, such as dielectric passivation, vacuum transfer of nano-materials, and proper annealing.

(8B.2 - RER) 3:35pm, March 25th

Input-Data Dependence and Technology Trend of Soft Error Rate in Flip-Flop

SER trends across six Samsung automotive technologies (130, 28, 14, 8, 5, and 4 nm)

SET induced SER in local clock buffers (LCB) by alpha-, high-energy neutron, and thermal neutron irradiation tests

The SER in FFs decreases with technological advancements from 14 nm to 5 nm in bulk-FinFET technologies, driven by stable Qcrit levels, but increases from 5 nm to 4 nm due to a lower Qcrit in 4 nm FFs.

Identifies the mechanism limiting write endurance under the high-field regime of FeFET.

Experimental characterization to establish that anode hole injection (AHI) during program is the dominant cause of cycling induced breakdown.

(8C.1 - EM) 3:10pm, March 25th

Mechanism study of dielectric breakdown in FeFET with gate side charge injection

Current transport anisotropy in Graphene on SiC

Direct growth of MoS2 on 4H-SiC

Graphene for improved thermal management in GaN HEMTs

(9A.2– SiC) 9:35am, March 26th

Two-dimensional Materials and Wide Bandgap Semiconductors: Integration challenges and novel device applications

(9C.1 - CR) 9:10am, March 26th

Experimental- and Simulation-Based Analysis of SRAM Data Retention Voltage Degradation Under Consideration of Time-Dependent-Variability

Measured yield of commercial SRAM macros under time-dependent variability (BTI after different stress times)

Simulation framework, calibrated to measurements, to estimate SRAM macro yield under time-dependent variability

(10A.2 - PR) 11:15am, March 26th

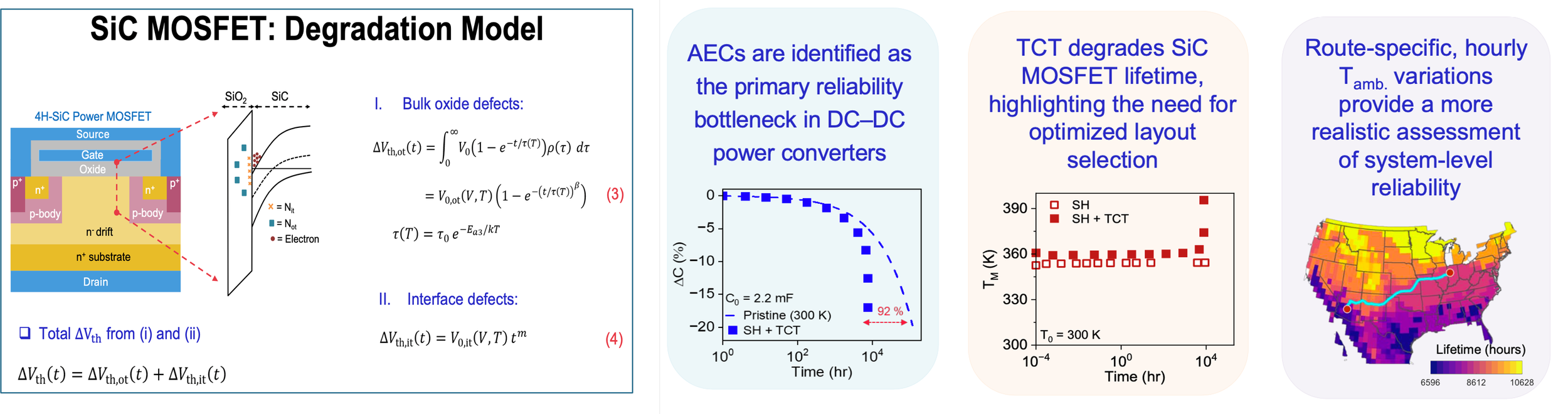

From Cornfields to Canyons: Route-Specific, Physics-Based, Predictive Reliability Modeling of DC–DC Power Converters

Reliability of System Electronics in Electric Vehicle Application

Physics Based Reliability Framework for DC-DC Power Converter

Coupled component aging induced by self-heating (SH) under shared electrical stress

Thermal cross-talk (TCT) between neighboring components.

System lifetimes determined by the temperature profiles of EV trips across the U.S.

(7C.1 - PR) 1:35pm, March 25th

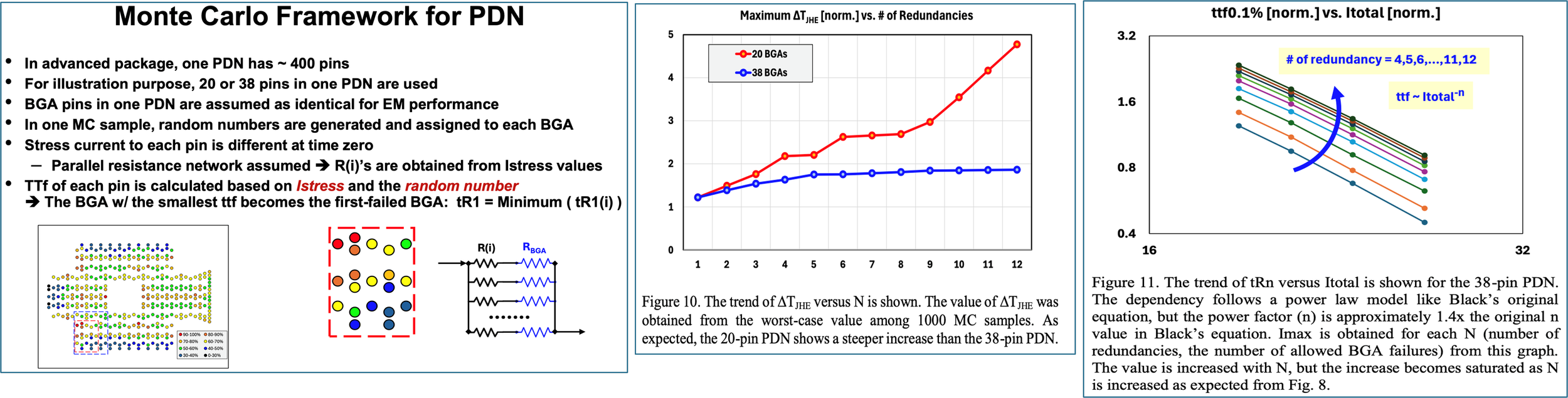

Monte Carlo-Based EM Lifetime Modeling of Power Delivery Network with Redundant BGA Pins

A Monte Carlo methodology that incorporates lognormal variability, parallel resistance networks, and dynamic current redistribution to realistically model EM behavior in power delivery networks (PDNs).

The approach captures the impact of redundancy on stress currents, IR drop, and ΔTJHE, demonstrating that redundancy can increase PDN EM lifetime by up to a factor of four compared with conventional methods.

(10A.3 - SER) 11:40am, March 26th

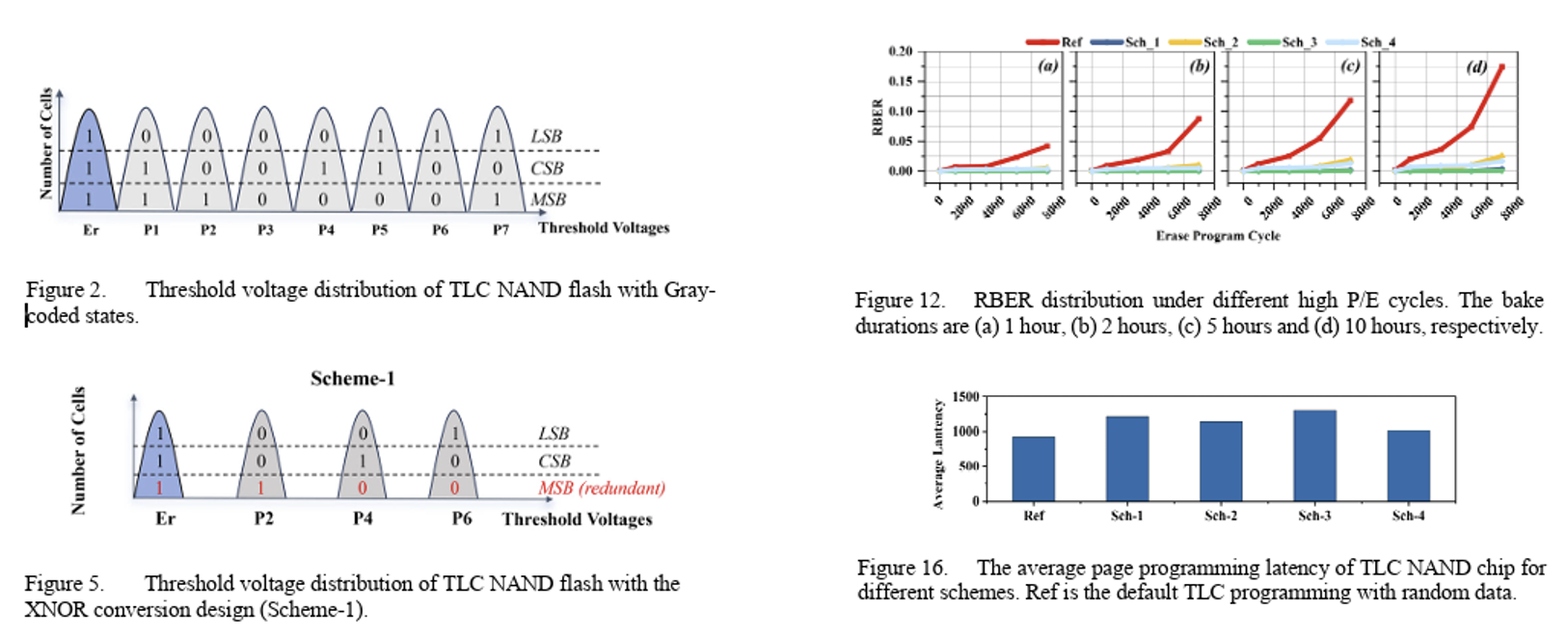

In-Place Backup: A Lightweight Strategy for On-Demand Reliability Enhancement in Multi-Bit-Per-Cell Solid-State Drives

Evaluates multiple schemes for redundant data encoding only where needed

Reduces read-disturb and retention errors

Imposes small performance overhead

(10C.4 - GD) 12:05 pm, March 26th

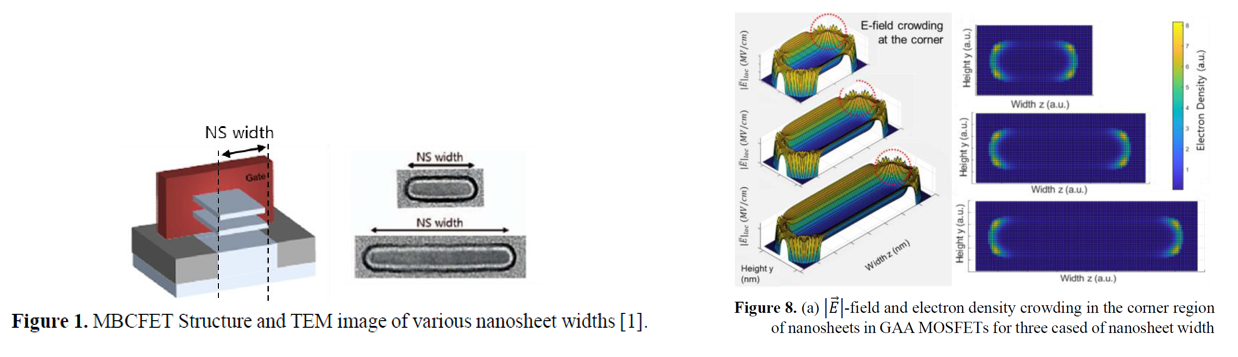

Analysis of the Width- and Area- Dependence Discrepancy in the GAA Structure TDDB using Numerical Simulation

This study finds that time-dependent dielectric breakdown (TDDB) of gate-all-around (GAA) devices is dominated by the corner regions due to electric-field crowding. This has direct implications for reliability-aware pathfinding involving the number and width of nanosheets (NS).

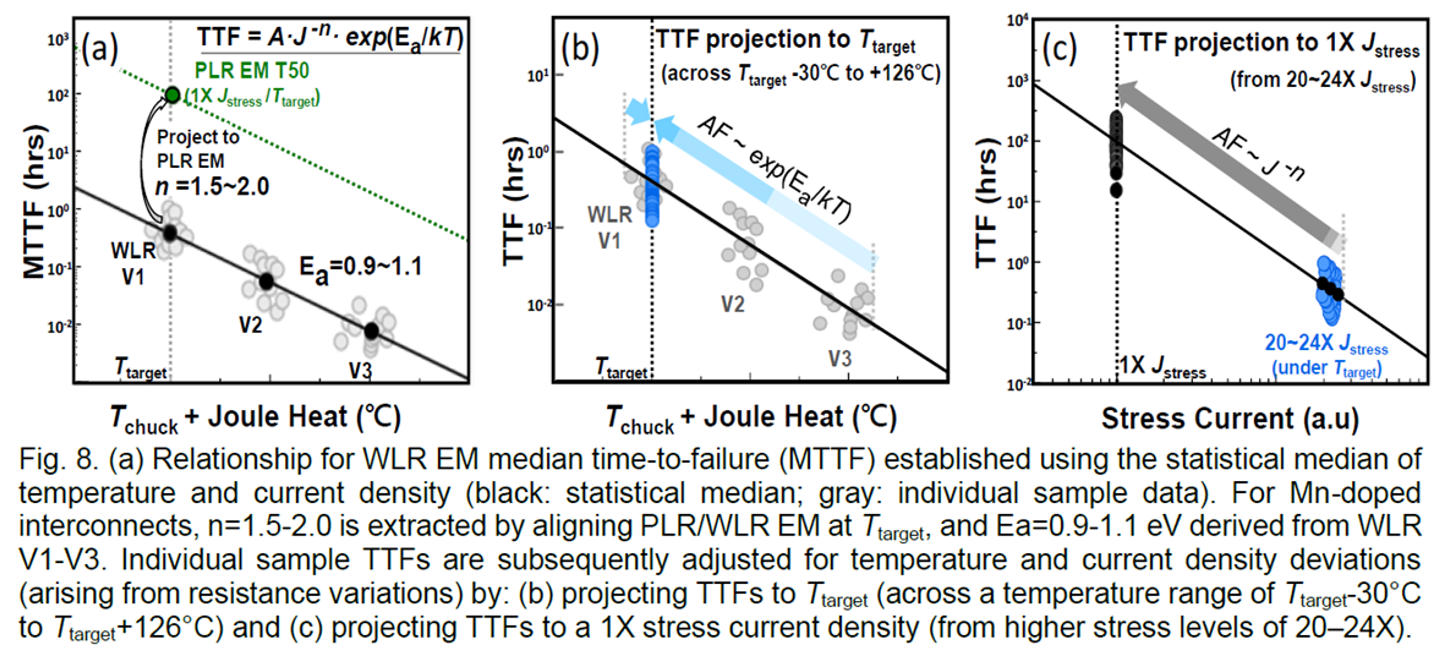

Demonstration of EM lifetime consistency between package-level and wafer-level under high temperature EM stress

(11A.1 - MB) 1:45 pm, March 26th

Exploring Cu Interface Reliability via Constant-Voltage WLR EM

(11B.1- RF) 1:45pm, March 26th

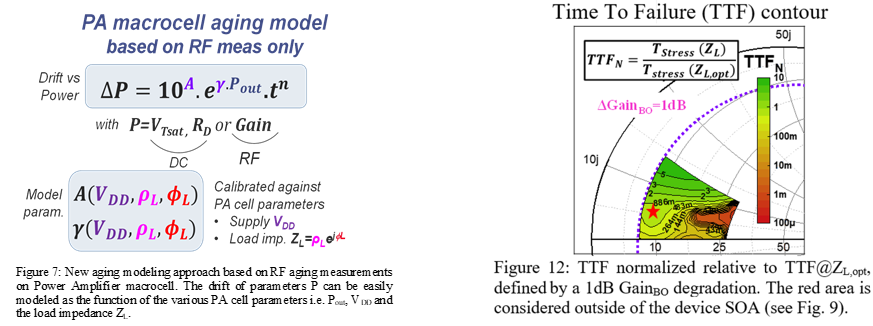

RF Aging Extensive Characterization & Modeling For Reliability-Aware Power Amplifier Design

Novel methodology to estimate transistor HCI degradation under RF mismatch, using extensive RF stresses at different bias and load impedance conditions.

(11C.1 - MR) 1:45 pm, March 26th

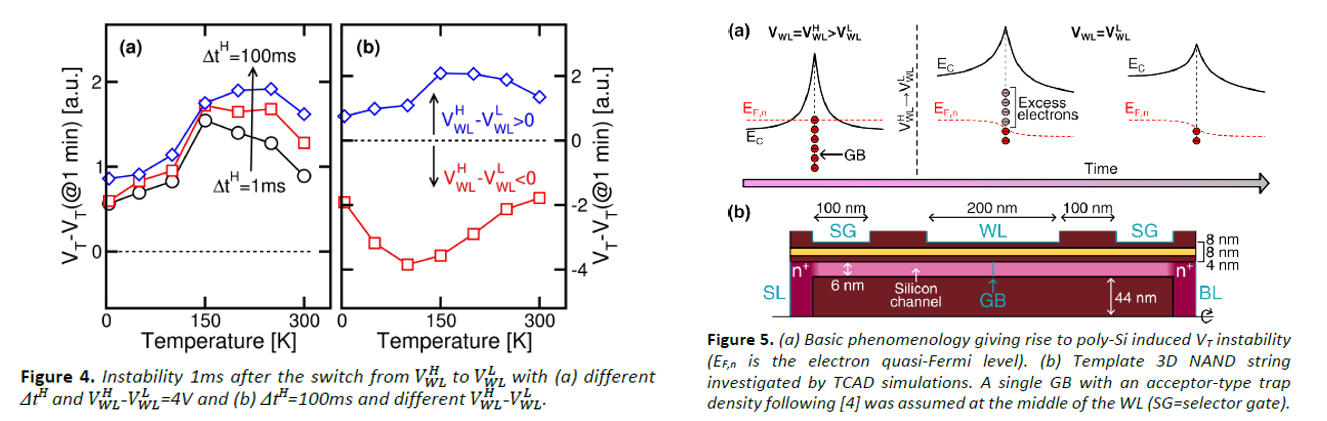

Poly-Si Channel-Induced Time Instability of 3D NAND Flash Cell Threshold-Voltage: A Comprehensive Temperature Analysis

The threshold-voltage instability in 3D NAND is studied due to temperature-dependent grain-boundary charge trapping.

(11C.3 - MR) 2:35 pm, March 26th

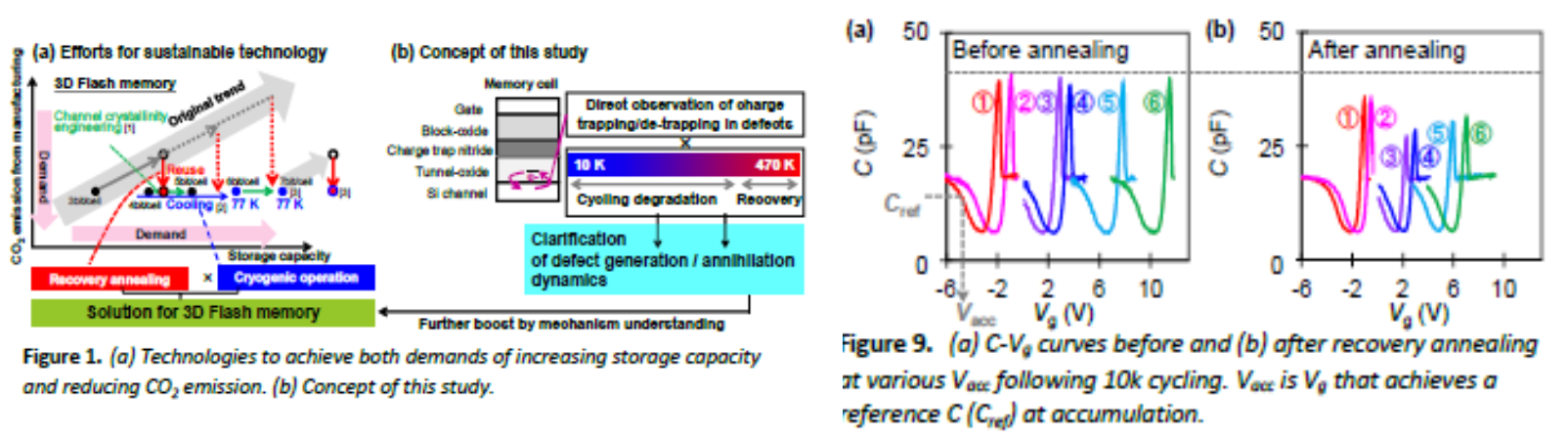

Clarification of Defect Generation and Annihilation Dynamics in MONOS Cells for Realization of Sustainable 3D Flash Memory with Cryogenic Operation and Recovery Annealing

Cryogenic operation suppresses hydrogen-related defect generation in 3D MONOS flash cells, and effective recovery annealing requires defects to remain neutral thus improving lifetime.